|

|

|

zurück |

Übersicht |

vorwärts

zurück |

Übersicht |

vorwärts

01 |

02 |

03 |

04 |

05 |

06 |

07 |

08 |

09 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

27 – Testverfahren in der Leiterplattenfertigung

In der Leiterplattenfertigung gibt es verschiedene Prüfmethoden, um die fertigen Leiterplatten zu testen. Hier ein Überblick über die relevanten Prüfverfahren.

Visuelle Kontrolle

Eine visuelle Kontrolle wird immer durchgeführt. Allerdings lassen sich so nicht alle Fehlerquellen erkennen. Fehler in Durchkontaktierungen können ebenso wenig erkannt werden wie Haarrisse oder Mikrokurzschlüsse. Zudem ist die visuelle Kontrolle fehlerbehaftet, da auch offensichtliche Fehler nach einer Weile gerne übersehen werden.

Elektrischer Test

Der elektrische Test testet Verbindungen von A nach B. Man unterscheidet Flying Probe (Fingertester) und Adaptertest.

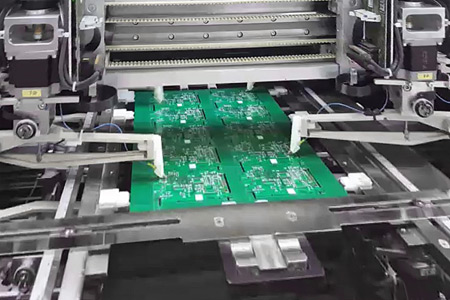

Flying Probe

Der Fingertest eignet sich besonders für enge Pad-Abstände, ist jedoch sehr zeitintensiv.

Daher wird Flying Probe gerne bei Mustern und Kleinserien eingesetzt, wobei nur ein Testprogramm benötigt wird.

Abb. 1 – Flying Probe

|

|

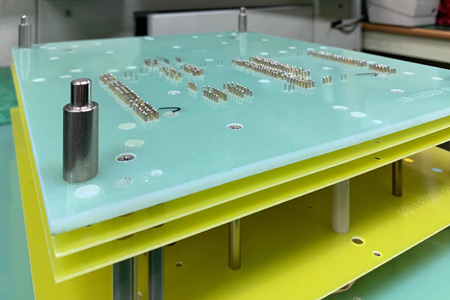

Adaptertest

Er ist aufwändiger, da ein auf die Leiterplatte abgestimmter Nadeladapter erforderlich ist. Dadurch lassen sich alle Verbindungen auf einmal testen und es dauert nur einen Bruchteil der Zeit gegenüber dem Flying Probe. Beim elektrischen Test wird zudem auf fehlerhafte Verbindungen getestet, z. B Kurzschlüsse durch Ätzfehler. Abb. 2 – Nadeladapter

|

AOI-Test

Beim AOI-Test – Automated Optical Inspection – handelt es sich um eine Kontrolle während der Fertigung im Sinne eines Soll-Ist-Vergleichs. Dazu wird die Leiterplatte mit gespeicherten Bildern des Soll-Zustands verglichen. Dadruch lassen sich nach dem Strukturieren Fehler auf Innen- und Außenlagen feststellen. Der Einsatz des AOI hängt in der Regel von den verwendeten Leiterbahnstrukturen ab.

Hochspannungstest

Beim Hochspannungstest gibt es 2 verschiedene Testverfahren.

HV-DC-Test

Der HV-DC-Test misst den Isolationswiderstand zwischen 2 Leitern oder Messpunkten. Dies kann beim elektrischen Test erfolgen. Deshalb werden hier auch Widerstandsgrenzwerte vorgegeben, bei dem das System Alarm schlägt. Die Testspannung kann hier bis zu mehrere Hundert Volt betragen.

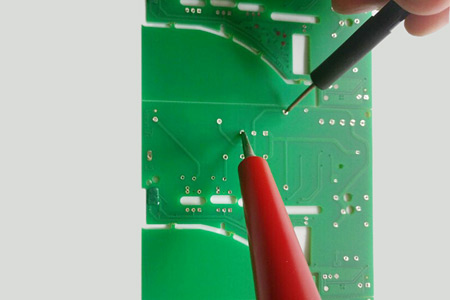

HV-AC-Test

Beim HV-AC-Test, auch dielektrischer Test genannt, wird die Spannungsfestigkeit (Isolation) zwischen Leitern getestet. Dazu wird eine hohe Spannung (>1000 V) an die Messpunkte angelegt und kontrolliert, ob es zu Durchschlägen und/oder Kriechströmen kommt. Üblich sind Stichproben und nicht die Prüfung des ganzen Produktionsloses.

Abb. 3, rechts – HV-AC-Test

|

|

|

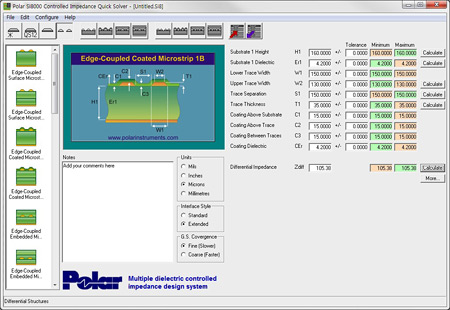

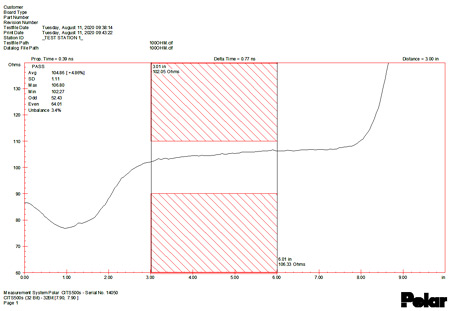

Impedanzkontrolle

Die Impedanzkontrolle misst den Scheinwiderstand von Leiterbahnen. Das ist gerade bei High-Speed-Verbindungen (Hochfrequenzanwendungen) wichtig. Dazu wird der Lagenaufbau vorab simuliert und gegebenenfalls angepasst. Die Software erstellt auch die benötigten Gerberdaten für den Coupon, an dem die Impedanzmessung später vorgenommen wird. Die Messungen werden normalerweise nicht an der Leiterplatte selbst, sondern am Coupon durchgeführt (Abb. 4), der mit im Fertigungsnutzen liegt und die gleichen Leiterbahnstrukturen aufweist wie die Leiterplatte.

|

|

Abb. 4 – Simulation, Messcoupon und Impedanzmesskurve |

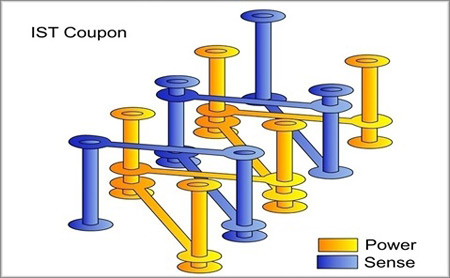

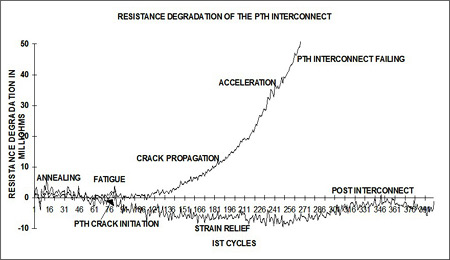

Interconnect Stress Test

Der Interconnect Stress Test (IST) ist ein Zuverlässigkeitstest, sozusagen eine Alternative zum Temperaturwechsel- oder Zyklen-Test. Auch hier wird der Test an einem speziellen Coupon durchgeführt. Vorteill: Hohe Zyklusrate, da der Coupon sehr schnell, in wenigen Minuten, aufgeheizt und abgekühlt werden kann. Nachteil: Relativ teures Messsystem. Daher werden solche Tests überwiegend in Bereichen eingesetzt, wo eine besonders hohe Zuverlässigkeit gefordert ist (Luft- und Raumfahrt, Medizintechnik etc.).

|

|

Abb. 5 – Aufbau, Messcoupon und Messkurve

(Bilder Copyright by Polar Instruments) |

4-Leiter- oder 4-Draht-Messung

Die Vierleiter- oder 4-Draht-Messung (4-Wire-Test) ist eine Widerstandsmessung für sehr kleine Widerstandswerte (< 0.1 Ohm). Dieses Verfahren kommt überwiegend im HDI-Bereich zum Einsatz, u.a. um Kupferfehlstellen in Micro-Vias aufzuspüren. Bei dieser Methode werden Messverfälschungen, verursacht durch Leitungs- und Übergangswiderstände, ausgeblendet.

LaTest®

Der LaTest® eignet sich ebenfalls, um Kupferfehlstellen in Vias und Einschnürungen (Mouse Bites) bei Leiterbahnen zu erkennen. Dazu wird auf das zu testende Netz ein Signal gegeben und an bestimmten Messpunkten wieder erfasst. Fehlstellen führen zu einer Phasenverschiebung des Signals und können somit erkannt werden. Auch dieses Verfahren ist sehr aufwändig und wird nur bei hochkomplexen Leiterplatten angewandt.

|

|